This is a generic DDS generator. Unlike a simple table lookup generator, it can interpolate between samples. Memory address size, memory word size and counter size are generic parameters. When interpolating, the generator can create higher resolution output than the memory word size from the lookup table. See the generic outputSize parameter in the source code for setting the resolution.

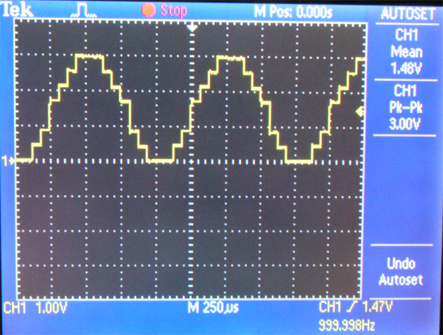

The example project outputs a sine signal on the LTC2624 DAC on the Spartan3E starter kit, but the VHDL code for the DDS entity should be portable to other FPGAs as well. For demonstrating the interpolating function, the lookup table has 16 entries, with 3 bit word size. This is the non-interpolated output:

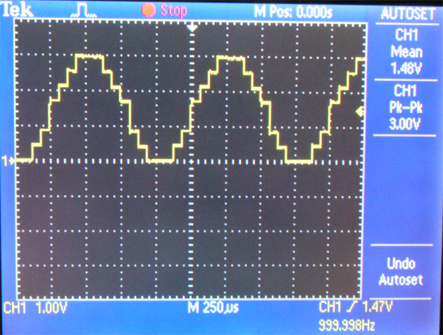

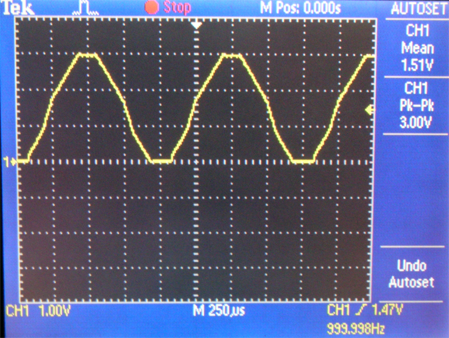

If you push the north-button on the Spartan3E development board, you can see how it will be interpolated with 8 bits output word size:

In the software directory there is a Lisp program to generate higher resolution and bigger lookup tables. You can delete some wait cycles, if you don't plan want to use BRAM and if you have a faster DAC.

Xilinx ISE WebPACK 9.2 project, including all VHDL source code files